🧠 RV32I vs PicoRV32 — Visual Diagrams (Deep Mapping) 🟣 1. RV32I Single-Cycle (Your Diagram Style) 🔎 How to read it: Everything happens in parallel…

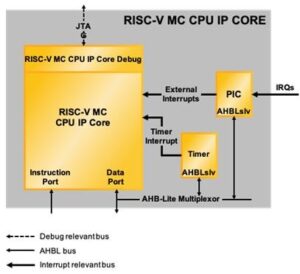

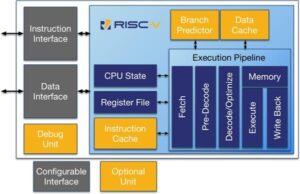

— here’s a clear, no-BS PicoRV32 tutorial to get you from “what is this” → “I can run it on FPGA / simulate it”. 🧠…

🚀 RV32I Tutorial #2: What is a Register File? Why Every CPU Needs It If RV32I defines what a CPU can do, then the…

🚀 RV32I Tutorial #1: What is RV32I? The Real Starting Point of a CPU Most people think CPUs understand code. They don’t. A CPU only…

Here’s a practical, no-fluff RV32I FPGA implementation roadmap — focused on getting you from zero → running code on hardware. hase 0 — Setup (1…

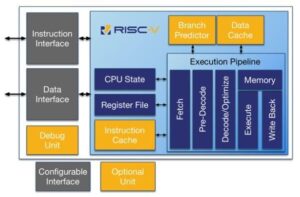

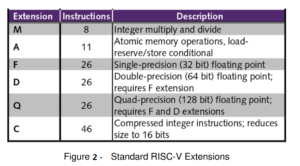

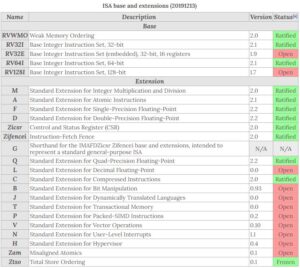

Article 1: Introduction to RISC-V – Why Learn It What is RISC-V and why it is an open Instruction Set Architecture (ISA) Modular design (RV32I…

Full Beginner Guide: How to Build a RISC-V CPU on an FPGA (2026 Edition) Building a RISC-V CPU on an FPGA is one of the…

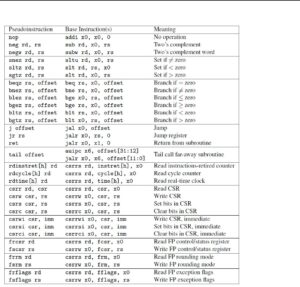

RISC-V Pseudo-Instruction Lookup Table Assembler Pseudo-instructions The assembler implements a number of convenience psuedo-instructions that are formed from instructions in the base ISA, but have…

This article will start with the I-Type integer register instructions and provide a detailed introduction to each assembly instruction and its specific implementation. 1. I-type…

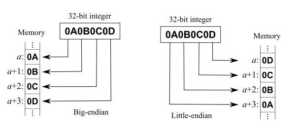

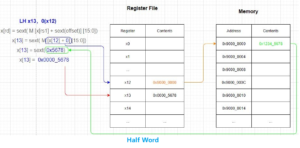

1. RISC-V Instruction Address Alignment For load/store instructions, the address of the data in memory should be aligned. If accessing 32-bit data, the memory address…

1. Load Store Instructions RV32I is a load-store architecture. Only load and store instructions can access memory and peripherals (registers inside the CPU can only…

1.Control Transfer Instruction In RV32I, control transfer instructions are mainly divided into two categories: unconditional jump and conditional jump. 2. Unconditional Jump Instructions Unconditional…

The register-register instruction format can directly operate on the data in registers without involving memory read or write operations, making it faster. R-Type instructions are…

The two U-type instructions introduced here operate on the program counter (PC) rather than the general-purpose registers (x0-x31), and are represented by the AUIPC opcode.…

This article will continue to introduce the remaining integer register-immediate instructions in the I-type (here it is the shift instruction). Figure 1 shows a shift…

This article will start with the I-Type integer register instructions and provide a detailed introduction to each assembly instruction and its specific implementation. I-type Integer…

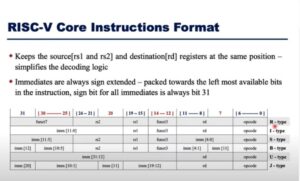

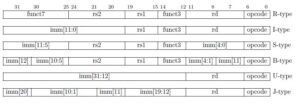

1.RISC-V Introduction the Origin of RISC-V, and the Features of RISC-V RISC-V Instruction Set Architecture Features and Classification RISC-V Instruction Set Encoding Structure, Features and…

1.RISC-V Instruction Set Explanation RISC-V is an open and free instruction set architecture widely used in processors and embedded systems. The RISC-V instruction set follows…

1. Instruction Set Encoding This article will continue the introduction of RISC-V and introduce the encoding structure of the RISC-V instruction set, as well as…

1.RISC-V Instruction Set Architecture Features The RISC-V instruction set has standard 32-bit architecture as well as 64-bit and 128-bit architectures. The general-purpose registers in the…